Copyright© 2009 by Chiphomer Technology Limited Page 1 of 22

# 3.1 Watt Fully Differential Audio Power Amplifier with Internal Feedback Resistors

# FEATURES

- Fully differential amplifier

- Improved PSRR at 217Hz

- Power output at 5.0V, 10% THD, 3 Ω (DFN8 only)

- Power output at 5.0V, 1% THD, 8  $\Omega$

- Ultra low shutdown current

- Improved pop & click circuitry eliminates noises during turn-on and turn-off transitions

- Thermal overload protection circuitry

- Unity-gain stable

- External gain configuration capability

- Available in space-saving packages: CSP9, MSOP8 and DFN8

- RoHS compliant and 100% lead(Pb)-free

# APPLICATIONS

- Wireless handsets

- Portable audio devices

- PDAs

- Notebook computers

# DESCRIPTION

The CP2296 is a fully differential audio power amplifier designed for demanding audio applications. It is capable of delivering 3.1 watt of continuous average power to a  $3\Omega$  BTL load with less than 10% distortion (THD+N) from a 5V battery voltage. It operates from 2.2V to 5.5V.

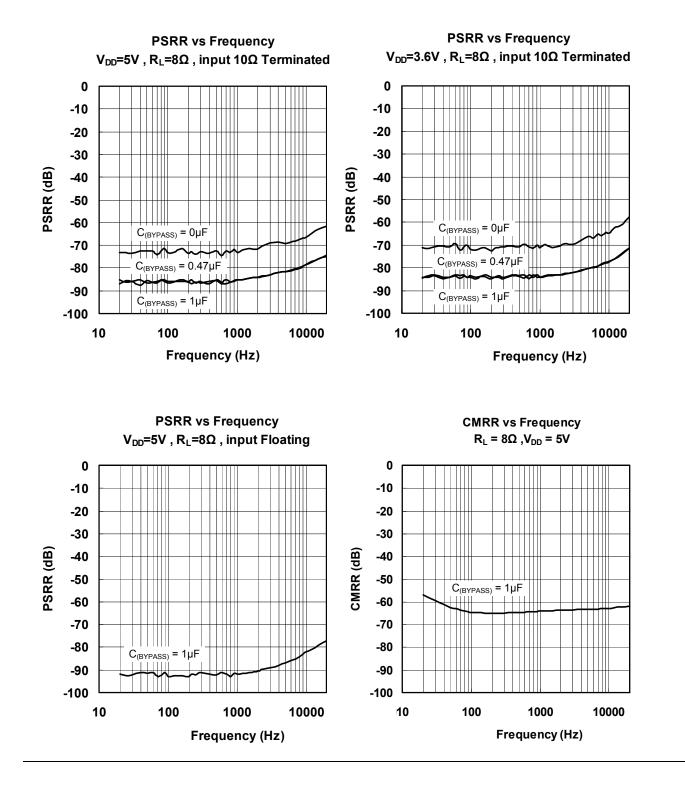

Features like -86dB PSRR at 217Hz, improved RF-rectification immunity, the space-saving CSP9, DFN8 and MSOP8 packages, the advanced pop & click circuitry, a minimal count of external components and low-power shutdown mode make CP2296 ideal for wireless handsets.

The CP2296 is unity-gain stable, and the gain can be configured by external input resistors and internal feedback resistors.

-86dB (typ)

3.1W (typ)

1.36W (typ)

0.01µA (typ)

-40°C~85°C

DFN8 封装 3mm x 3mm -40℃~85℃

DFN8 封装 2mm x 2mm -40℃~85℃

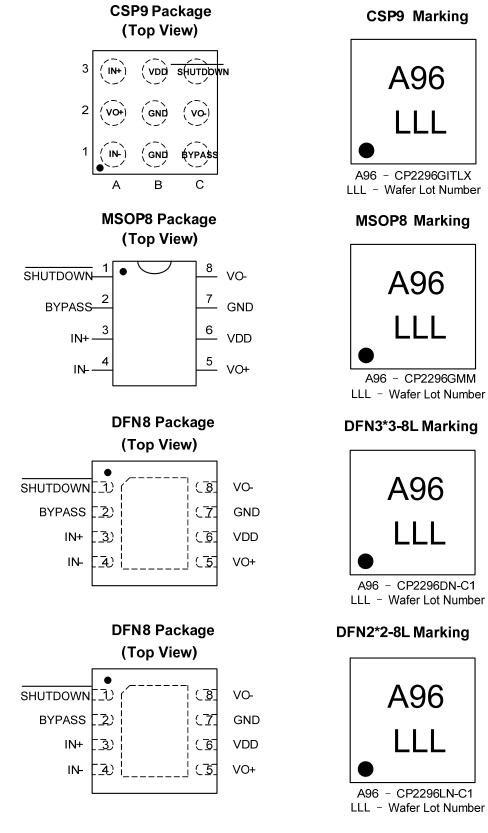

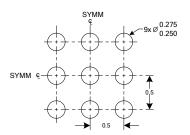

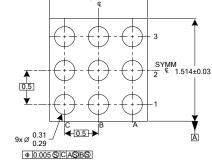

# **Pin Configuration**

Figure 1 Pin Configuration of CP2296

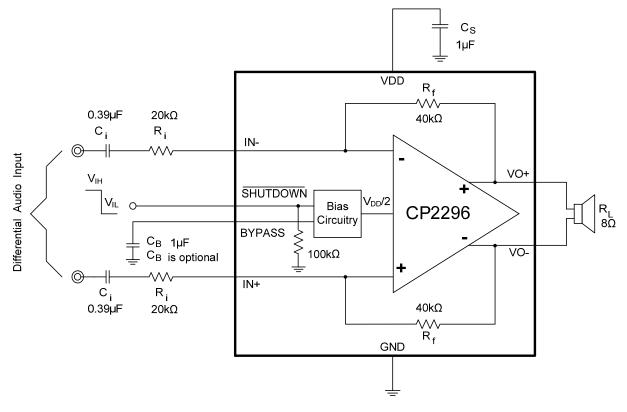

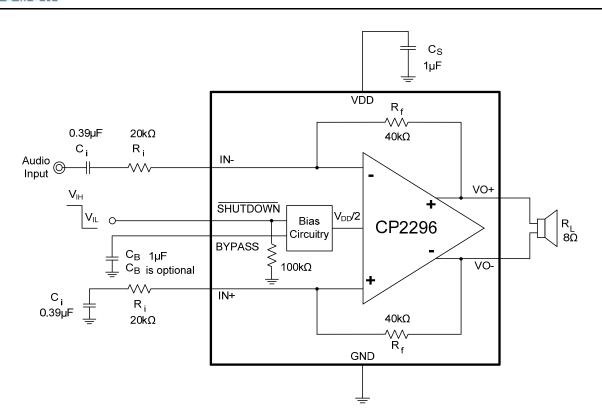

# TYPICAL APPLICATION

Figure 2 CP2296 Typical application Circuit

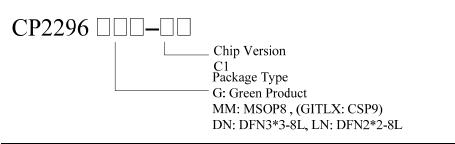

# **ORDERING INFORMATION**

| Order Number | Temperature<br>Range | Package    | RoHS | Marking    | Shipping<br>Type          |

|--------------|----------------------|------------|------|------------|---------------------------|

| CP2296GITLX  | -40℃~85℃             | CSP9       | Y    | A96<br>LLL | 3000 pcs /<br>Tape & Reel |

| CP2296GMM    | -40℃~85℃             | MSOP8      | Y    | A96<br>LLL | 3000 pcs /<br>Tape & Reel |

| CP2296DN-C1  | -40℃~85℃             | DFN 3*3-8L | Y    | A96<br>LLL | 3000 pcs /<br>Tape & Reel |

| CP2296LN-C1  | -40℃~85℃             | DFN 2*2-8L | Y    | A96<br>LLL | 3000 pcs /<br>Tape & Reel |

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Parameter                                        | Unit               |

|--------------------------------------------------|--------------------|

| Supply voltage (VDD)                             | -0.3V to 6.0V      |

| Input voltage                                    | -0.3V to VDD+0.3V  |

| Power dissipation <sup>(2)</sup>                 | Internally Limited |

| Package Thermal Resistance $\theta_{JA}$ (CSP9)  | 220°C/W            |

| Package Thermal Resistance $\theta_{JA}$ (MSOP8) | 190°C/W            |

| Package Thermal Resistance $\theta_{JC}$ (MSOP8) | 56℃/W              |

| Package Thermal Resistance $\theta_{JA}$ (DFN8)  | 63℃/W              |

| Package Thermal Resistance $\theta_{JC}$ (DFN8)  | 12℃/W              |

| Maximum Junction Temperature                     | <b>150</b> ℃       |

| Storage Temperature Range                        | -65℃ to 150℃       |

| Lead Temperature (Soldering 10 Seconds)          | <b>260</b> ℃       |

| ESD Rating <sup>(3)</sup>                        |                    |

| Human Body Model                                 | 8000V              |

| Machine Model                                    | 200V               |

| Latch-up Immunity                                | 200mA              |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX}=(T_{JMAX}-T_A)/\theta_{JA}$  or the number given in Absolute Maximum Ratings, whichever is lower.

- (3) The human body model is a 100pF capacitor discharged through a 1.5kΩ resistor into each pin. The machine model is a 200pF capacitor discharged directly into each pin.

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                     | Unit         |  |  |

|-----------------------------------------------|--------------|--|--|

| Supply voltage (VDD)                          | 2.2V to 5.5V |  |  |

| Operating temperature range (T <sub>A</sub> ) | -40℃ to 85℃  |  |  |

# **ELECTRICAL CHARACTERISTICS**

Test Condition:  $V_{DD}$ =5.0V,T<sub>A</sub>=25°C, A<sub>V</sub>=1V/V, The following specifications apply for 8 $\Omega$  load (unless otherwise specified)

| Symbol            | Parameter                            | Conditions                                                                             | Min                           | Тур                           | Max                           | Unit |  |

|-------------------|--------------------------------------|----------------------------------------------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|------|--|

| I <sub>DD</sub>   | Quiescent Power                      | VIN=0V, no load                                                                        |                               | 3                             | 8                             | — mA |  |

|                   | Supply Current                       | VIN=0V, $R_L=8\Omega$                                                                  |                               | 4                             | 10                            |      |  |

| I <sub>SD</sub>   | Shutdown Current                     | V <sub>SHUTDOWN</sub> =GND                                                             |                               | 0.01                          | 1                             | μA   |  |

| Po                |                                      | THD=1%(max); f=1kHz<br>R <sub>L</sub> =3Ω<br>R <sub>L</sub> =4Ω<br>R <sub>L</sub> =8Ω  |                               | 2.45<br>2.22<br>1.36          |                               | W    |  |

|                   | Output Power                         | THD=10%(max); f=1kHz<br>R <sub>L</sub> =3Ω<br>R <sub>L</sub> =4Ω<br>R <sub>L</sub> =8Ω |                               | 3.1<br>2.6<br>1.7             |                               | W    |  |

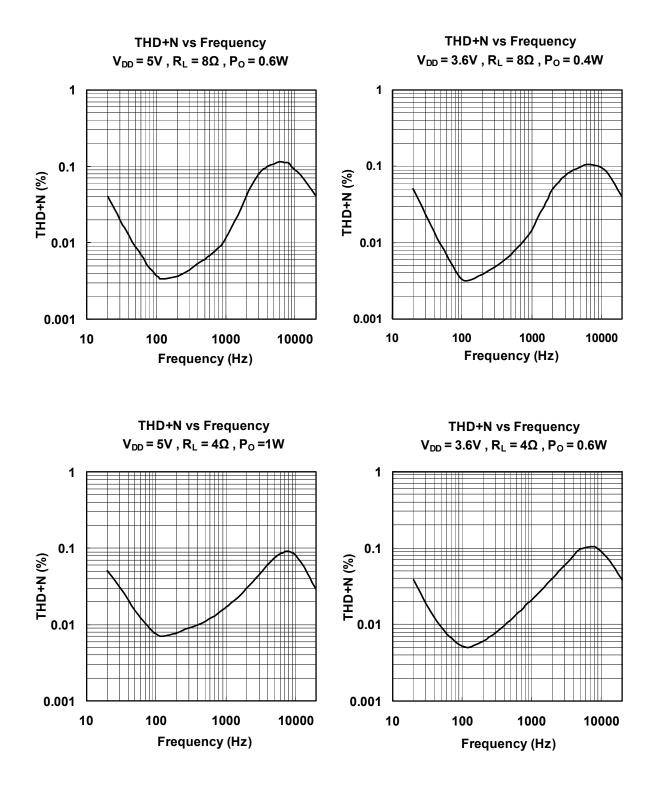

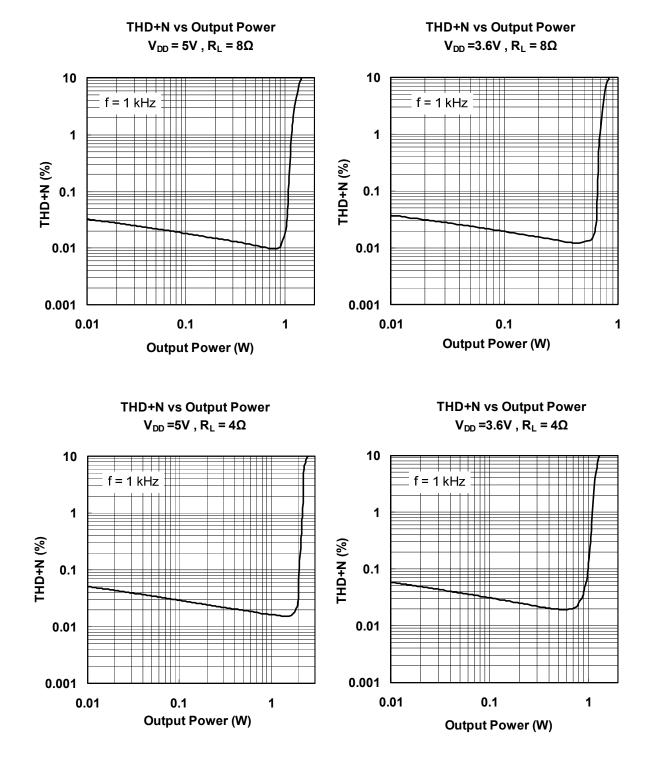

| THD+N             | Total Harmonic<br>Distortion + Noise | P <sub>o</sub> =1Wrms; f=1kHz                                                          |                               | 0.02                          |                               | %    |  |

|                   | Power Supply<br>Rejection Ratio      | V <sub>ripple</sub> =200mV sine p-p                                                    |                               |                               |                               |      |  |

| PSRR              |                                      | f=217Hz (Note1)                                                                        |                               | -86                           |                               | dB   |  |

|                   |                                      | f=1KHz (Note1)                                                                         |                               | -83                           |                               |      |  |

| SNR               | Signal to Noise<br>Ratio             | P <sub>o</sub> =1Wrms; f=1kHz                                                          |                               | 105                           |                               | dB   |  |

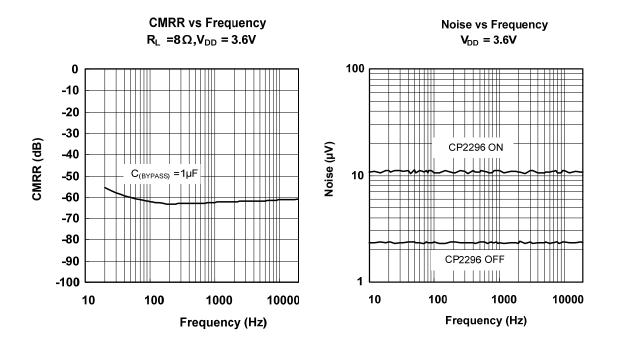

| CMRR              | Common Mode<br>Rejection Ratio       | f=217Hz V <sub>CM</sub> =200mV <sub>PP</sub>                                           |                               | -65                           |                               | dB   |  |

| V <sub>os</sub>   | Output Offset                        | VIN=0V                                                                                 |                               | 1                             | 10                            | mV   |  |

| V <sub>SDIH</sub> | Shutdown Voltage<br>Input High       |                                                                                        | 1.5                           |                               |                               | V    |  |

| $V_{\text{SDIL}}$ | Shutdown Voltage<br>Input Low        |                                                                                        |                               |                               | 0.5                           | V    |  |

| A <sub>V</sub>    | Closed Loop Gain                     |                                                                                        | <u>36kΩ</u><br>R <sub>i</sub> | <u>40kΩ</u><br>R <sub>i</sub> | <u>44kΩ</u><br>R <sub>i</sub> | V/V  |  |

| $R_{SD}$          | Resistance from shutdown to GND      |                                                                                        |                               | 100                           |                               | kΩ   |  |

**Note1:**  $10\Omega$  terminated input

Test Condition:  $V_{DD}$ =3.6V,T<sub>A</sub>=25°C, A<sub>V</sub>=1V/V, The following specifications apply for 8 $\Omega$  load (unless otherwise specified)

| Symbol            | Parameter                            | Conditions                                                                            | Min                           | Тур                           | Max                           | Unit |  |

|-------------------|--------------------------------------|---------------------------------------------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|------|--|

| I <sub>DD</sub>   | Quiescent Power                      | VIN=0V, no load                                                                       |                               | 2.5                           | 7                             | mA   |  |

| IDD               | Supply Current                       | VIN=0V, $R_L=8\Omega$                                                                 |                               | 3.5                           | 9                             |      |  |

| I <sub>SD</sub>   | Shutdown Current                     | V <sub>SHUTDOWN</sub> =GND                                                            |                               | 0.01                          | 1                             | μA   |  |

| Po                | Output Power                         | THD=1%(max); f=1kHz<br>R <sub>L</sub> =3Ω<br>R <sub>L</sub> =4Ω<br>R <sub>L</sub> =8Ω |                               | 1.22<br>1.1<br>0.72           |                               | W    |  |

| THD+N             | Total Harmonic<br>Distortion + Noise | P <sub>o</sub> =0.5Wrms; f=1kHz                                                       |                               | 0.02                          |                               | %    |  |

|                   | Power Supply<br>Rejection Ratio      | V <sub>ripple</sub> =200mV sine p-p                                                   | DmV sine p-p                  |                               |                               |      |  |

| PSRR              |                                      | f=217Hz (Note1)                                                                       |                               | -83                           |                               | dB   |  |

|                   |                                      | f=1KHz (Note1)                                                                        |                               | -80                           |                               |      |  |

| SNR               | Signal to Noise<br>Ratio             | P <sub>o</sub> =0.5Wrms; f=1kHz                                                       |                               | 100                           |                               | dB   |  |

| CMRR              | Common Mode<br>Rejection Ratio       | f=217Hz $V_{CM}$ =200m $V_{PP}$                                                       |                               | -63                           |                               | dB   |  |

| V <sub>os</sub>   | Output Offset                        | VIN=0V                                                                                |                               | 1                             | 10                            | mV   |  |

| V <sub>SDIH</sub> | Shutdown Voltage<br>Input High       |                                                                                       | 1.5                           |                               |                               | V    |  |

| V <sub>SDIL</sub> | Shutdown Voltage<br>Input Low        |                                                                                       |                               |                               | 0.5                           | V    |  |

| A <sub>V</sub>    | Closed Loop Gain                     |                                                                                       | <u>36kΩ</u><br>R <sub>i</sub> | <u>40kΩ</u><br>R <sub>i</sub> | <u>44kΩ</u><br>R <sub>i</sub> | V/V  |  |

| $R_{SD}$          | Resistance from shutdown to GND      |                                                                                       |                               | 100                           |                               | kΩ   |  |

**Note1:** 10Ω terminated input

# **PIN DEFINITION**

| CSP9  | DFN8 | MSOP8 | Symbol   | Description                                                                                                                 |  |

|-------|------|-------|----------|-----------------------------------------------------------------------------------------------------------------------------|--|

| C3    | 1    | 1     | SHUTDOWN | Shutdown Pin, active low.                                                                                                   |  |

| C1    | 2    | 2     | BYPASS   | Common mode voltage. Connect a bypass capacitor to GND for common mode voltage filtering. The bypass capacitor is optional. |  |

| A3    | 3    | 3     | IN+      | Positive differential input.                                                                                                |  |

| A1    | 4    | 4     | IN-      | Negative differential input.                                                                                                |  |

| A2    | 5    | 5     | VO+      | Positive differential output.                                                                                               |  |

| B3    | 6    | 6     | VDD      | Power supply.                                                                                                               |  |

| B1,B2 | 7    | 7     | GND      | Ground.                                                                                                                     |  |

| C2    | 8    | 8     | VO-      | Negative differential output.                                                                                               |  |

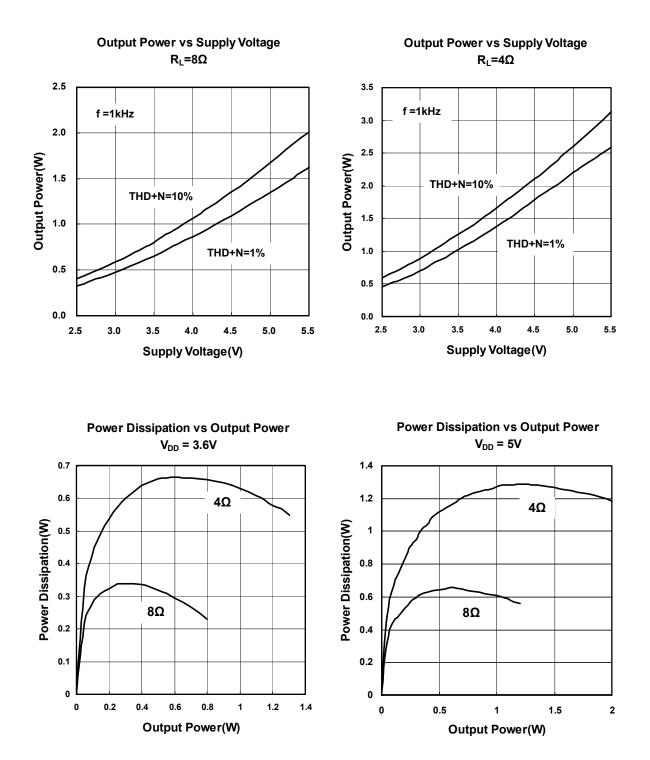

# **TYPICAL OPERATING CHARACTERISTICS**

ID

# **APPLICATION INFORMATION**

### **Fully Differential Amplifier Description**

The CP2296 is a fully differential amplifier with differential inputs and outputs. The fully differential amplifier consists of a differential amplifier and a common mode feedback amplifier. The differential amplifier ensures that the amplifier outputs a differential voltage that is equal to the differential input times the gain. The common mode feedback ensures that the common-mode voltage at the output is biased around VDD/2 regardless of the common-mode voltage at the input.

The CP2296 provides a "bridged mode" output configuration (bridge-tied-load, BTL). This means the output signals at Vo+ and Vo- that are 180° out of phase with respect to each other. Bridged mode operation is different from the single-ended output configuration that connects the load between the amplifier output and ground. A bridged amplifier design has distinct advantages over the single-ended output configuration: it provides differential drive to the load, thus doubling maximum possible output swing for a specific supply voltage. Four times the output power is possible compared with a single-ended output configuration under the same conditions. This increase in attainable output power assumes that the amplifier is not current limited or clipped.

### Advantages of Fully Differential Amplifier

Input and output coupling capacitor not required: A fully differential amplifier with good CMRR, the CP2296 allows the input signal to be biased at voltage other than mid-supply of the CP2296, the common-mode feedback circuit adjusts for it, and the outputs are still biased at mid-supply of the CP2296.

Mid-supply bypass capacitor,  $C_{\text{BYPASS}}$  not required: The fully differential amplifier does not require a bypass capacitor. It is because any shift in the mid-supply affects both positive and negative channels equally and cancels at the differential output. However, removing the bypass capacitor slightly worsens power supply rejection ration, but a slightly decrease of PSRR may be acceptable when an additional component can be eliminated.

Better RF-immunity: GSM handsets save power by turning on and shutting off the RF transmitter at a rate of 217Hz. The transmitted signal is picked-up on input and output traces. The fully differential amplifier reduces the RF rectification much better than the typical audio amplifier.

## Applications

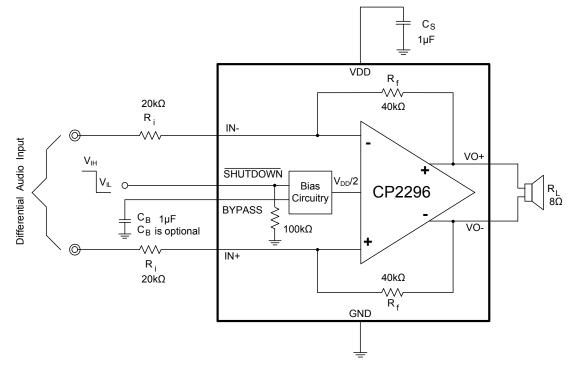

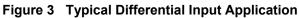

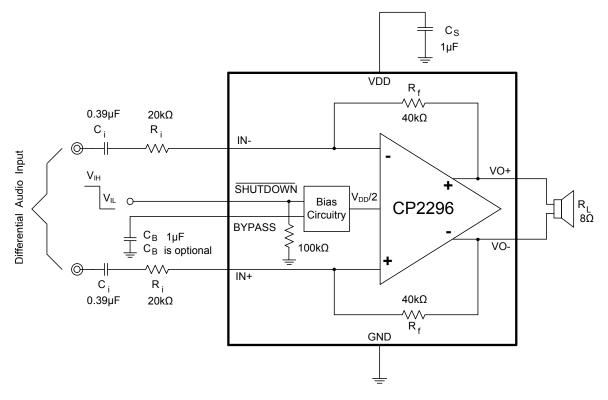

From Figure 3 to Figure 5 show application schematics for differential and single-ended inputs.

Figure 4 Differential Input Application With Input Capacitors

Figure 5 Single-Ended Input Application

### **Proper Selection of external Components**

#### Input Resistor (R<sub>i</sub>)

The input (R<sub>i</sub>) and internal feedback resistors,  $R_f$ =40k $\Omega$ , set the gain of the amplifier according to Equation 1:

(1)

(2)

Gain =

$$40k\Omega/R_i$$

In order to optimize the THD+N and SNR performance, The CP2296 should be used in low closed-loop gain configuration.  $R_i$  should be in range from  $1k\Omega$  to  $100k\Omega$ . Resistor matching is very important for fully differential amplifiers. The balance of the output on the common mode voltage depends on matched ratios of the resistors. CMRR, PSRR, and the second harmonic distortion is increased if resistor is not matched. Therefore, it is recommended to use 1% tolerance resistors or better to keep the performance optimized.

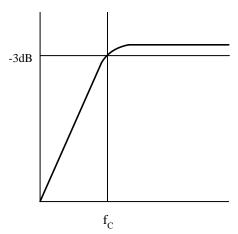

### Input Capacitor (C<sub>i</sub>)

The input coupling capacitor blocks the input DC voltage. The CP2296 does not require input coupling capacitors if using a differential input source that is biased from 0.5V to VDD-0.8V. Use 1% tolerance or better resistors if not using input coupling capacitors. In the single-ended input application an input coupling capacitor,  $C_i$ , is required to allow the amplifier to bias the input signal to the proper dc level. The  $C_i$  and  $R_i$  form a high-pass filter with the corner frequency determined in Equation 2:

$$f_{c} = \frac{1}{2\pi R_{i}C_{i}}$$

Special care should be taken to the value of  $C_i$  because it directly affects the low frequency performance of the system. For example, assuming  $R_i$  is  $20k\Omega$  and the specification calls for a flat response down to 100Hz. From Equation 2,  $C_i$  is 0.08uF, so  $C_i$  would likely choose a value in the range of  $0.068\mu F$  to  $0.47\mu F$ . A further consideration for  $C_i$  is the leakage path from the input source through the input network ( $R_i$ ,  $C_i$ ) and the feedback resistor ( $R_f$ ) to the load. This leakage current creates a DC offset voltage that reduces useful headroom, especially in high gain applications. For this reason, a ceramic capacitor is the best choice.

#### Bypass Capacitor (CBYPASS) and Start-Up Time

Connecting a capacitor to BYPASS pin filters any noise into this pin and increases the PSRR performance.  $C_{BYPASS}$  also determines the rise time of VO+ and VO-, the larger the capacitor, the slower the rise time, the CP2296 start to work after the  $C_{BYPASS}$  voltage reaches the mid-supply voltage. This capacitor can also minimize the pop & click noise during turn-on and turn-off transitions, the larger the capacitor, the smaller the pop & click noise,  $1\mu$ F capacitor is recommended for  $C_{BYPASS}$ .

#### Decoupling Capacitor (C<sub>S</sub>)

Power supply decoupling is critical for low THD+N and high PSRR performance. A low equivalent-series-resistance (ESR) ceramic capacitor, typically  $0.1\mu$ F to  $1\mu$ F, placed as close as possible to VDD pin makes the device work better. For filtering lower frequency noise signals, a  $10\mu$ F or greater capacitor placed near the audio power amplifier also helps, but it is not required in most applications because of the high PSRR of this device.

#### Using Low-ESR Capacitors

Low-ESR capacitors are recommended. A real capacitor can be modeled simply as a resistor in series with an ideal capacitor. The voltage drop across this resistor minimizes the beneficial effects of the capacitor in the circuit. The lower the equivalent value of this resistance the more the real capacitor behaves like an ideal capacitor.

### **Power Dissipation**

Power dissipation is a major concern when designing a successful amplifier, whether the amplifier is bridged or single-ended. Equation 3 states the maximum power dissipation point for a single-ended amplifier operating at a given supply voltage and driving a specified output load.

$$P_{DMAX} = \frac{V_{DD}^{2}}{2\pi^{2}R_{L}}$$

Single-Ended (3)

However, a direct consequence of the increased power delivered to the load by a bridge amplifier is an increase in internal power dissipation versus a single-ended amplifier operating at the same conditions.

$$P_{DMAX} = 4 * \frac{V_{DD}^{2}}{2\pi^{2}R_{L}} \qquad \text{Bridge-Ended} \qquad (4)$$

Since the CP2296 has bridged outputs, the maximum internal power dissipation is 4 times that of a single-ended amplifier. Even with this substantial increasing in power dissipation, the CP2296 does not require additional heat-sinking under most operating conditions and output loading. From Equation 4,

assuming a 5V power supply and an  $8\Omega$  load, the maximum power dissipation point is 625mW. The maximum power dissipation point obtained from Equation 4 must not be greater than the power dissipation results from Equation 5:

$$\mathsf{P}_{\mathsf{DMAX}} = (\mathsf{T}_{\mathsf{JMAX}} - \mathsf{T}_{\mathsf{A}}) / \theta_{\mathsf{JA}}$$

(5)

Depending on the ambient temperature, TA, of the system surroundings, Equation 5 can be used to find the maximum internal power dissipation supported by the IC packaging. If the result of Equation 4 is greater than that of Equation 5, then either the supply voltage must be decreased, the load impedance increased, the ambient temperature reduced, or the  $\theta_{JA}$  reduced with heat-sinking. In many cases, larger traces near the output, VDD, and GND pins can be used to lower the  $\theta_{JA}$ . The larger areas of copper provide a form of heat-sinking allowing higher power dissipation. Recall that internal power dissipation is a function of output power. If the typical operation is not around the maximum power dissipation point, the CP2296 can operate at higher ambient temperatures.

### **Shutdown Function**

In order to reduce power consumption while not in use, the CP2296 contains shutdown circuitry that is used to turn off the amplifier's bias circuitry. The shutdown pin should be tied to a definite voltage to avoid unwanted state changes. In many applications, a microcontroller or microprocessor output is used to control the shutdown circuitry, which provides a quick, smooth transition to shutdown.

### **Board Layout Consideration**

The residual resistance of the PCB trace between the amplifier output pins and the speaker causes a voltage drop, which results in power dissipated in the PCB trace and not in the speaker as desired. Therefore, to maintain the highest speaker power dissipation and widest output voltage swing, PCB trace that connects the amplifier output pins to the speaker must be as wide as possible.

Poor power supply regulation adversely affects maximum output power. A poorly regulated supply's output voltage decreases with increasing load current. Reduced supply voltage causes decreased headroom, output signal clipping, and reduced output power. Even with tightly regulated supplies, power supply trace resistance creates the same effects as poor supply regulation. Therefore, making the power supply trace as wide as possible helps to maintain full output voltage swing.

It is very important to keep the CP2296 external components very close to the CP2296 to limit noise pickup.

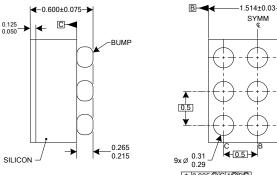

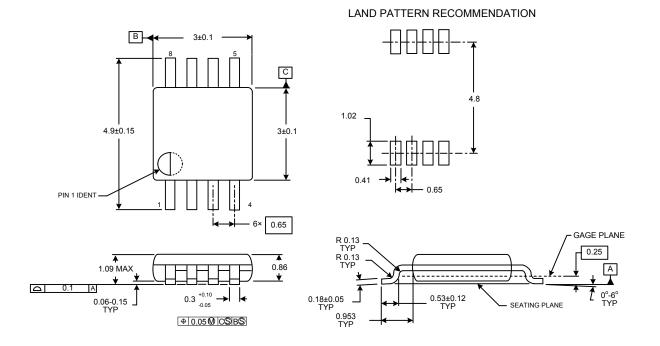

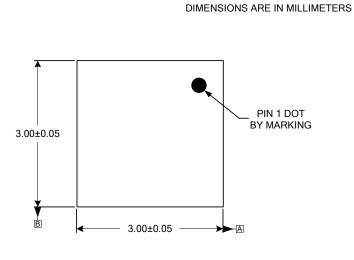

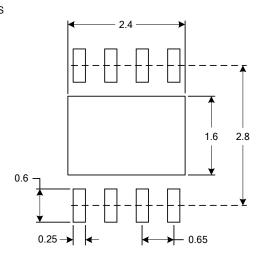

# **PACKAGE DESCRIPTION**

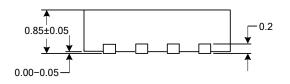

LAND PATTERN RECOMMENDATION

DIMENSIONS ARE IN MILLIMETERS

TOP SIDE COATING BUMP A1 CORNER

CSP9 Package Part Number CP2296GITLX

Package Description (continued)

### DIMENSIONS ARE IN MILLIMETERS

MSOP8 Package Part Number CP2296GMM

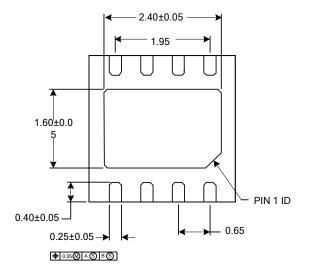

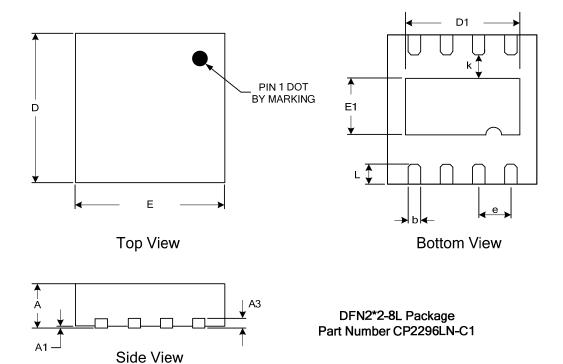

### Package Description (continued)

LAND PATTERN RECOMMENDATION

DFN3\*3-8L Package Part Number CP2296DN-C1

### Package Description (continued)

| Symbol | Dimensions In Millimeters |             | Dimensions In Inches |             |  |

|--------|---------------------------|-------------|----------------------|-------------|--|

| Symbol | Min                       | Max         | Min                  | Max         |  |

| A      | 0.700/0.800               | 0.800/0.900 | 0.028/0.031          | 0.031/0.035 |  |

| A1     | 0.000                     | 0.050       | 0.000                | 0.002       |  |

| A3     | 0.203                     | 3REF        | 0.008REF             |             |  |

| D      | 1.900                     | 2.100       | 0.075                | 0.083       |  |

| E      | 1.900                     | 2.100       | 0.075                | 0.083       |  |

| D1     | 1.100                     | 1.300       | 0.043                | 0.051       |  |

| E1     | 0.500                     | 0.700       | 0.020                | 0.028       |  |

| k      | 0.200MIN                  |             | 0.008MIN             |             |  |

| b      | 0.180                     | 0.300       | 0.007                | 0.012       |  |

| е      | 0.500                     | OTYP        | 0.020TYP             |             |  |

| L      | 0.250                     | 0.450       | 0.010                | 0.018       |  |

### **Copyright Information**

Copyright © 2009 by Chiphomer Technology Limited. All rights reserved.

This document is provided to the Chiphomer's customers as the product description, and contains information considered proprietary by Chiphomer Technology Limited. No part of this document may be copied, or reproduced in any form or by any means, or transferred to any third party without the written consent of Chiphomer.

The contents of this document may be revised without prior notice.

### **Contact with Chiphomer**

4F, Building D, 1618 Yishan Road Shanghai, 201103, P.R.C. Tel: (86)21-64014543 64058488 Fax: (86)21-64050030

Sale: sales@chiphomer.com Technical support: support@chiphomer.com Web site: www.chiphomer.com

Shenzhen Office:

10D, Building 2, Dushi Yangguang Garden CheGongMiao, Futian District, Shenzhen, 518048, P.R.C. Tel: (86)755-82046706, 82047789 Fax: (86)755-82046709